- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC18F4450T-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

dsPIC30F3010/3011

DS70141F-page 42

2010 Microchip Technology Inc.

4.2.3

MODULO ADDRESSING

APPLICABILITY

Modulo Addressing can be applied to the Effective

Address (EA) calculation associated with any W regis-

ter. It is important to realize that the address boundar-

ies check for addresses less than or greater than the

upper (for incrementing buffers) and lower (for decre-

menting buffers) boundary addresses (not just equal

to). Address changes may, therefore, jump beyond

boundaries and still be adjusted correctly.

4.3

Bit-Reversed Addressing

Bit-Reversed Addressing is intended to simplify data

re-ordering for radix-2 FFT algorithms. It is supported

by the X AGU for data writes only.

The modifier, which may be a constant value or register

contents, is regarded as having its bit order reversed.

The address source and destination are kept in normal

order. Thus, the only operand requiring reversal is the

modifier.

4.3.1

BIT-REVERSED ADDRESSING

IMPLEMENTATION

Bit-Reversed Addressing is enabled when:

1.

BWM (W register selection) in the MODCON

register is any value other than 15 (the stack can

not be accessed using Bit-Reversed

Addressing) and

2.

the BREN bit is set in the XBREV register and

3.

the addressing mode used is Register Indirect

with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is M = 2N bytes,

then the last ‘N’ bits of the data buffer start address

must be zeros.

XB<14:0> is the bit-reversed address modifier or ‘pivot

point’ which is typically a constant. In the case of an

FFT computation, its value is equal to half of the FFT

data buffer size.

When enabled, Bit-Reversed Addressing will only be

executed for Register Indirect with Pre-Increment or

Post-Increment

Addressing

and

word-sized

data

writes. It will not function for any other addressing

mode or for byte-sized data, and normal addresses will

be generated instead. When Bit-Reversed Addressing

is active, the W Address Pointer will always be added

to the address modifier (XB) and the offset associated

with the Register Indirect Addressing mode will be

ignored.

In

addition,

as

word-sized

data

is

a

requirement, the LSb of the EA is ignored (and always

clear).

If Bit-Reversed Addressing has already been enabled

by setting the BREN (XBREV<15>) bit, then a write to

the XBREV register should not be immediately followed

by an indirect read operation using the W register that

has been designated as the Bit-Reversed Pointer.

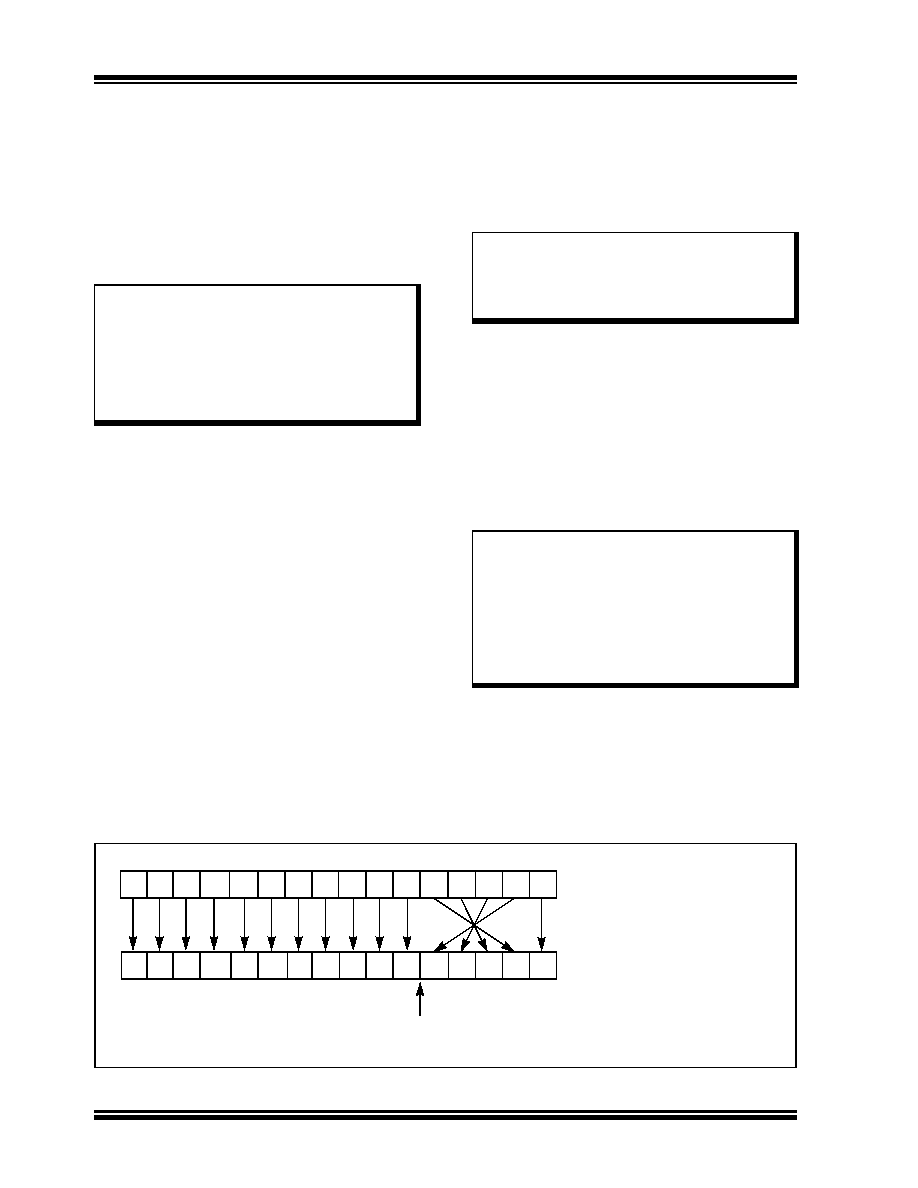

FIGURE 4-2:

BIT-REVERSED ADDRESS EXAMPLE

Note:

The modulo corrected effective address is

written back to the register only when Pre-

Modify or Post-Modify Addressing mode is

used to compute the effective address.

When an address offset (e.g., [W7 + W2])

is used, Modulo Addressing correction is

performed, but the contents of the register

remains unchanged.

Note:

All bit-reversed EA calculations assume

word-sized data (LSb of every EA is

always clear). The XB value is scaled

accordingly to generate compatible (byte)

addresses.

Note:

Modulo Addressing and Bit-Reversed

Addressing

should

not

be

enabled

together. In the event that the user

attempts

to

do

this,

Bit-Reversed

Addressing will assume priority when

active for the X WAGU, and X WAGU

Modulo Addressing will be disabled. How-

ever, Modulo Addressing will continue to

function in the X RAGU.

b3 b2 b1

0

b2 b3 b4

0

Bit Locations Swapped Left-to-Right

Around Center of Binary Value

Bit-Reversed Address

XB = 0x0008 for a 16-word Bit-Reversed Buffer

b7 b6 b5 b1

b7 b6 b5 b4

b11 b10 b9 b8

b15 b14 b13 b12

Sequential Address

Pivot Point

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4321T-I/ML

IC PIC MCU FLASH 4KX16 44QFN

PIC18F4221T-I/ML

IC PIC MCU FLASH 2KX16 44QFN

PIC18F2321T-I/ML

IC PIC MCU FLASH 4KX16 28QFN

PIC18F2221T-I/SO

IC PIC MCU FLASH 2KX16 28SOIC

PIC16LF1939-I/MV

IC MCU 8BIT 28KB FLASH 40-UQFN

PIC24F16KL402-I/SP

IC MCU 16BIT 16KB FLASH 28-SPDIP

PIC18F24J11-I/SS

IC PIC MCU FLASH 16K 2V 28-SSOP

PIC24F16KA101-I/SO

IC PIC MCU FLASH 16K 20-SOIC

相关代理商/技术参数

PIC18F4450T-I/PT

功能描述:8位微控制器 -MCU 16KB FL 768 RAM 34 I/O FS-USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-BL

制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB; Silicon Manufacturer:Powerlite Systems; Core Architecture:PIC; Kit Contents:Board; Features:Bootloader Programming, RS232 Connector for Boot-Loading and Serial Comms ;RoHS Compliant: Yes

PIC18F4455-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/P

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4458-I/ML

功能描述:8位微控制器 -MCU 24KB Flash 2KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT